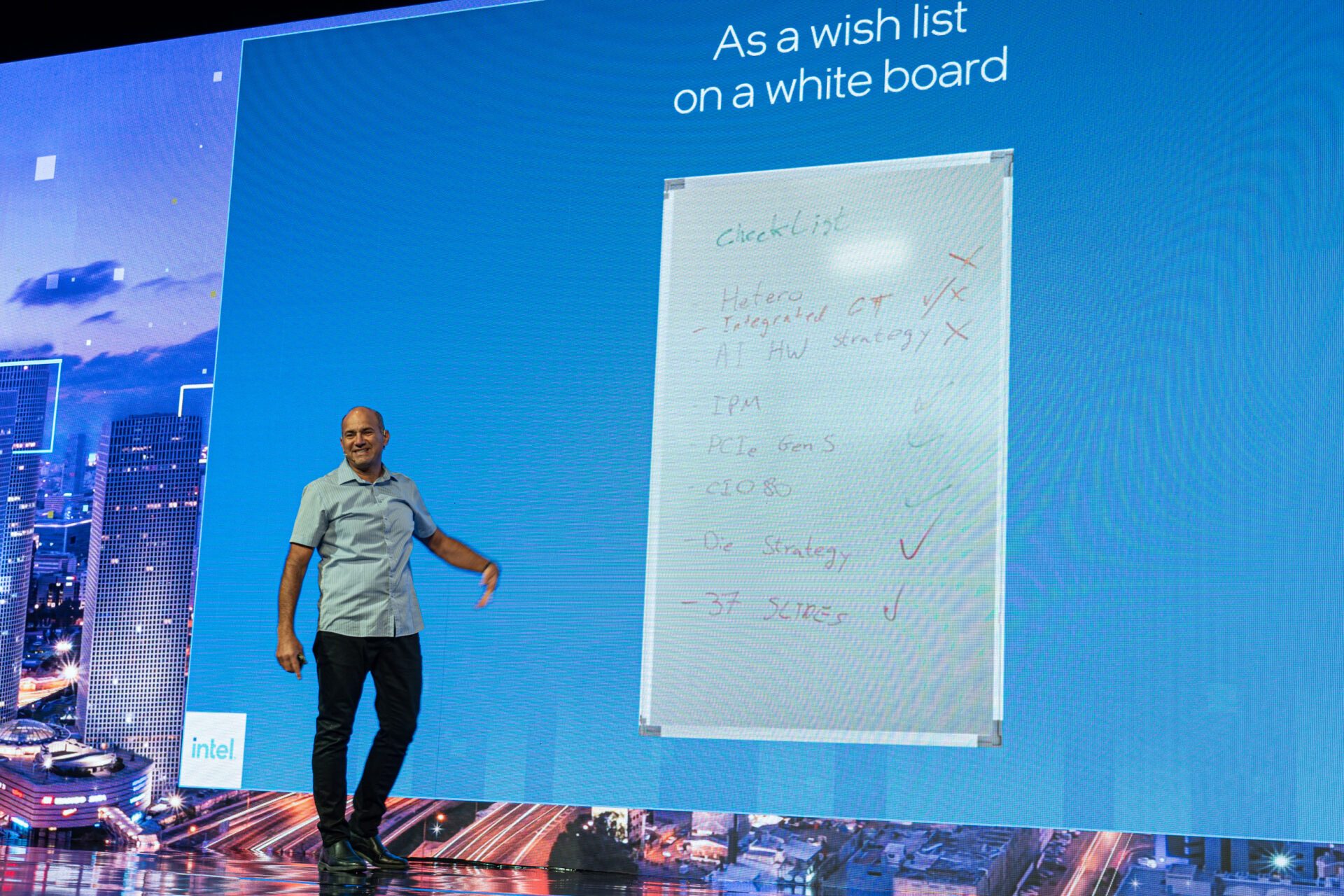

L’accouchement a duré trois ans. Et le bébé a trouvé un nom de combat : “Raptor Lake”, ou les processors grand public Core de 13d Intel generation. Des puses qui reprennent la philosophie de la previous generation Alder Lake: marier de gros cœurs Core performantes (les P-Cores) à une horde de cœurs CPU plus petits, mais energeticamente plus efficaces (les E-Cores). ” Le challenge d’Alder Lake, qui a peut-être échappé à certains commentators, était non seulement l’architecture hybride. Mais aussi et surtout that it is designed to be available in 16 variants for PC portables and desktops ranging from 9 W to 125 W ” said Issik Silas, vice president of Intel’s client computing group, based in Israel. Il raconte en clin d’œil ” que le siège n’était pas très chaud au début et que nous avons dû nous displacer aux Etats Unis pour vaincre les équipes dirigneantes! “.

At the head of his Israeli team, Isic Silas controls not only the development of the P-Core that is cooked locally, but also the integration of all the elements of this SoC. Faisant de cette generation un nouveau succes made in israel d’Intel, et aussi l’orgueil de M. Silas : ” Avec une architecture peaufinée, nous sommes capable de produire des puces 10 nm supérieures en puissance brute à des cuces gravées 5 nm “. Capable of reaching 6 GHz, Raptor Lake is not a new architecture, but an in-depth refinement of the existing one.

The gain of 15% from generation to generation is made on all plans: increase in frequencies, improvement in consumption and ratio perf/Watt, addition of new microcontrollers, work on the firmwareimplementation d’algorithmes entrainment par apprentissage machine (machine learning) to improve prechargement of instructions and behavior of applications, etc. Le tout, sur fund du COVID qui avait déjà affect le développement d’Alder Lake. Affecté, mais pas ralenti : « at the beginning of the pandemic in February 2020, nous avons converti en seulement quelques jours sept salles de conférences en labos techniques operationales afin de continuer à operér. Sans prendre de risque avec nas employés “.

Un nombre optimal de “gros” cœurs

When we read the technology sheet of the Raptor Lake processors already announced, an element jumps out of our eyes: if the number of cores is on the rise, it’s because Intel has already doubled the number of cores in terms of performance. Sans jamais ajouter un seul cœur hautes performances.

“ Nous avons surtout travaillé la partition énergétique de nos puces “, explicient en cœur Ran Berenson et Arik Ghon, des deux “cerveaux” aux commandes du développement des puces. ” Une des grosses diférences entre la 12d and others. 13d génération dont nous sommes fiers est la partie alimentation “, explain les deux ingénieurs. ” Pour la même consommation énergétique, les cœurs develop bien plus de puissance “, se félicitent-ils. “La clé de ces progrès était d’improvement l’énergie consommée par chaque traitement d’instruction. And quand on consider dans les details, on s’aperçoit que la plupart des bonnes applications use only two or four threads hautes performances. Et les applications qui use beaucoup de threads n’ont pas necessairement besoin de monter très haut en fréquence “, continued les deux experts.

Austrian lira : Generation Core 13e Raptor Lake: Comment Intel veut reprendre sa couronne de roi des PCs (September 2022)

On pourrait ici pointer du digt que les approches d’Intel et AMD vary notably à cause de la taille très différente de leurs cœurs. Intel’s high performance P-Cores are really big, AMD’s cores are tous de taille moyenne, Intel’s E-cores are really small. Here, each approach to its strengths and weaknesses. If AMD peut déployer plus de “gros” cœurs qu’Intel, les cœurs basse consommation d’Intel lui permettent de composer, avec ses deux cœurs différents, un plus grand nombre de puces. Il lui suffit de panacher ses cœurs selon la puissance – et la consommation énergétique – target.

x86 n’est pas une faiblesse et se nourrit des autres architectures

Tous les ans, on lit qu’ARM est le futur et que x86 est mort. Intel et AMD ne peuvent evidently pas être de cet avis, mais pour une fois nous avons eu accès aux ingénieurs à la source de la microarchitecture. Ils ont pu nous réponder sur l’impact négatif que x86 et ses éléments de retrocompatibilité aurait sur les performances. ” Nous nous posons la question à chaque génération ,” replied Adi Yoaz, Director of Architecture at Core. ” Tout est affaire de puissance par surface de puce. La question étant, est-ce que cette compatibilité nous handicape beaucoup? Combien devons-nous ”payer” pour cela ? According to us estimates, cela pourrait Aller de 5% and others jusqu’à 10% de pertes de puissance. Mais en moyenne, c’est generally plus proche des 5%. Et nous avons plein de techniques pour contourner ces limitations “, assure l’ingénieur. Here is the son of a colleague Ron Berenson shows this moment: ” Au final, il nous serait plus difficile de nous débarrasser de ces anciennes instructions que de les conserver “.

Austrian lira : Alder Lake, “la plus grosse évolution du x86 depuis dix ans” : Intel unveils the guts of its next Core processors (October 2021)

Quant au rapport que le Champion des instructions x86 entretient avec ARM et RISC V, la réalité est qu’elles s’influencent beaucoup les unes les autres. Repoussant gentiment l’idea d’un départ de zéro de x86, Adi Yoaz explains posément que ” le monde des semi-conducteurs s’influence. Et sachez que si nous apportons beaucoup aux autres architectures, nous nous inspirons aussi d’elles, comme pour les instructions à taille fixe. Ou pour la taille des registers. Person n’est en vase clos dans ce monde »assures l’ingénieur.

Une affaire de chimie et de cooperation

Interrogé à propos de l’impact des avancées de la chimie et des nodes industriels de miniaturization dans la conception logic des puces, Adi Yoaz is categorical ” C’est absolument criticism. La connexion que nous entretenons avec nos colleges qui travailten sur la chemie et les materials, ainsi que ceux du the process (la finesse de fabrication, ndlr) est fundamental. Tous ces éléments influencent directement les designs des puces “, expl.-t-il.

Avant d’ajouter que si une poignée d’ingénieurs a dans ses mains la conception du brouillon de la puce, dès que labor est lanzée, le flux de travail est enormément distribué. Non seulement entre les différences spécialists, mais surtout entre les différences sites d’Intel. “ The new P-Core “Raptor Cove” and the pilotage of the SoC assembly were made here, in Israel. More Intel is a global enterprise and the whole world participates: E-Core it is developed in Austin (Texas) and others. GPU à Folsom (California) “, détaille-t-il.

Tick-Tock is back (non, pas le réseau social)

Avant même que vous ingurgitiez des heures de videos verticales sur Tik-Tok, the world of processors is already beating to the rhythm of Tick et des Tock d’Intel. Une dynamique de launch de procesors qui correctait à une alternance entre le launch d’une nouvelle architecture (tock) et le passage à une finesse de gravure plus fine (tick). The transition from 22 nm to 14 nm and the arrival of the Skylake architecture made this dynamic fly in the open with a simple “refresh” between 2015 and 2020. Since his arrival at the head of Intel, his new PDG, Pat Gelsinger, (artisan de nombre de procesadores dans les années 80/90) a décidé de renouer avec le modèle tick-tock ou tout du moins avec une plus grande fréquence d’execution. En allant même jusqu’à entreprise son entreprise sur cinq améliorations de la finesse de gravure (Intel 7, Intel 4, Intel 3, Intel 20A and Intel 18A) en quatre ans !

Cette pression de l’accelération des développement cycles dear à Pat Gelsinger, les équipes de développement la resentent. Car tout cela prend du temps. ” Le cycle de développement d’un produit prend en gros trois ans. Mais pour Raptor Lake, nous avons mis seulement 30 mois », s’enorgueillit Isic Silas. Il parle de l’effet boule de neige qui s’est déroulé les six premiers mois: “ Au tout début, il ya ten personnes au maximum sur le projet. Six mois après, ce sont des dizaines de milliers de personnes qui sont implicates! “. One of the elements that allows Raptor Lake to be faster than Alder Lake comes from an external partner: Microsoft. ” When we define products, we talk to our clients and partners. Windows 10 ne prenait pas en charge les architectures Hétérogènes de cœurs. Nous avons parlé avec Microsoft, qui l’a integré dans Windows 11 “. L’arrivée de Raptor Lake a donc pu se faire plus rapidement.

Un futur de chiplets (et des défis à surmonter)

Comme AMD avec ses ” chiplets “, Intel will soon assemble SoCs with heterogeneous bricks – an approach that the Santa Clara society calls for disaggregation. Une démarche qui vise surtout à limiter la montée du prix des puces liée à l’augmentation des costs de la miniaturisation. Concrètment, il s’agit d’amelioreur des returns en utilisant de petits morceaux de puses – une très grande puce d’une surface N coûte plus cher à produire que quatre puces occupying la même surface totale.

Intel devrait passer à cette technologie pour la 14d “Meteor Lake” generation. Mais alors que pour les analysts extérieurs, dont nous sommes modestement, cette partition reste la panacée, dans les faits cette fragmentation en plusieurs puces a des limites. “Le premier défi est de trouver l’équilibre parfait entre les éléments”, explains Ady Yoaz. ” This goes further than the performance report by Watt. C’est un rapport plus complexe perf/énergie/surface/coût. Et s’il ya des advantages à couper des morceaux de puces, il ya aussi des costs dans les techniques d’assemblage telles que Foveros chez nous “, explains l’ingénieur. Il considre cependant bien que la technologie represents une pièce du futur des puces. Au même titre que ” l’ajout d’accélérateurs, que ce soit pour la video, la blockchainle chiffrement, etc. ». Dans un contexte où Intel est à la chasse aux optimisations, les ingénieurs d’Intel n’ont pas fini de se retrousser les manches pour en mettre toujours plus dans leurs puces. Pour aller plus vit. Toujours plus vite.